Mila - Quebec AI Institute and McGill University

Mila - Quebec AI Institute and McGill UniversityI am a PhD Student in Electrical & Computer Engineering at Mila - Quebec AI Institute and McGill University, working with Prof. Boris Vaisband and Prof. Warren Gross. My research focuses on Machine Learning for Electronic Design Automation (ML for EDA), with particular interests in Graph Representation Learning, Timing Analysis, and Physical Design.

Education

-

Mila - Quebec AI Institute and McGill UniversityPhD Student in Electrical & Computer EngineeringTopic: Machine Learning for Electronic Design AutomationJan. 2023 - Present

Mila - Quebec AI Institute and McGill UniversityPhD Student in Electrical & Computer EngineeringTopic: Machine Learning for Electronic Design AutomationJan. 2023 - Present -

North South UniversityBachelor of Science in Computer Science & EngineeringMay 2017 - April 2021

North South UniversityBachelor of Science in Computer Science & EngineeringMay 2017 - April 2021

Experience

-

Noah's Ark LabMontreal, CanadaAssociate ML Researcher, InternGraph Representation Learning for Performance PredictionDec. 2024 - June 2025

Noah's Ark LabMontreal, CanadaAssociate ML Researcher, InternGraph Representation Learning for Performance PredictionDec. 2024 - June 2025 -

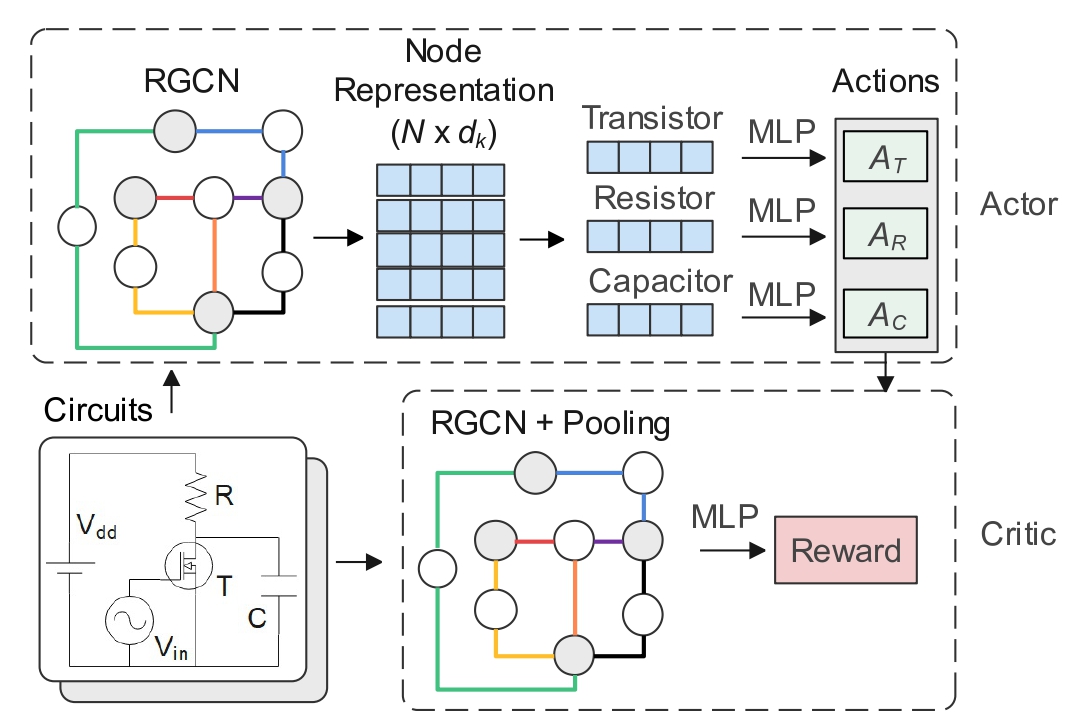

Noah's Ark LabMontreal, CanadaAssociate ML Researcher, InternReinforcement Learning and Graph Neural Networks for Analog Transistor SizingMay 2023 - Oct. 2023

Noah's Ark LabMontreal, CanadaAssociate ML Researcher, InternReinforcement Learning and Graph Neural Networks for Analog Transistor SizingMay 2023 - Oct. 2023 -

Hilinkz Ltd.Dhaka, BangladeshChief Executive OfficerLed team, designed architecture, developed web applicationsFeb. 2021 - Dec. 2022

Hilinkz Ltd.Dhaka, BangladeshChief Executive OfficerLed team, designed architecture, developed web applicationsFeb. 2021 - Dec. 2022 -

HURU Technologies Ltd.Dhaka, BangladeshSoftware Engineer InternDeveloped web app for Digital Service Hiring SolutionOct. 2020 - Jan. 2021

HURU Technologies Ltd.Dhaka, BangladeshSoftware Engineer InternDeveloped web app for Digital Service Hiring SolutionOct. 2020 - Jan. 2021

Honors & Awards

-

DAC Young Fellow2025

-

MEDA Award - McGill Engineering Doctoral Award2023

-

50% Merit-based Tuition Waiver, North South University2017

Research Interests

- Graph Representation Learning

- Electronic Design Automation

- Timing Analysis

- Physical Design

- Machine Learning for EDA

Selected Publications

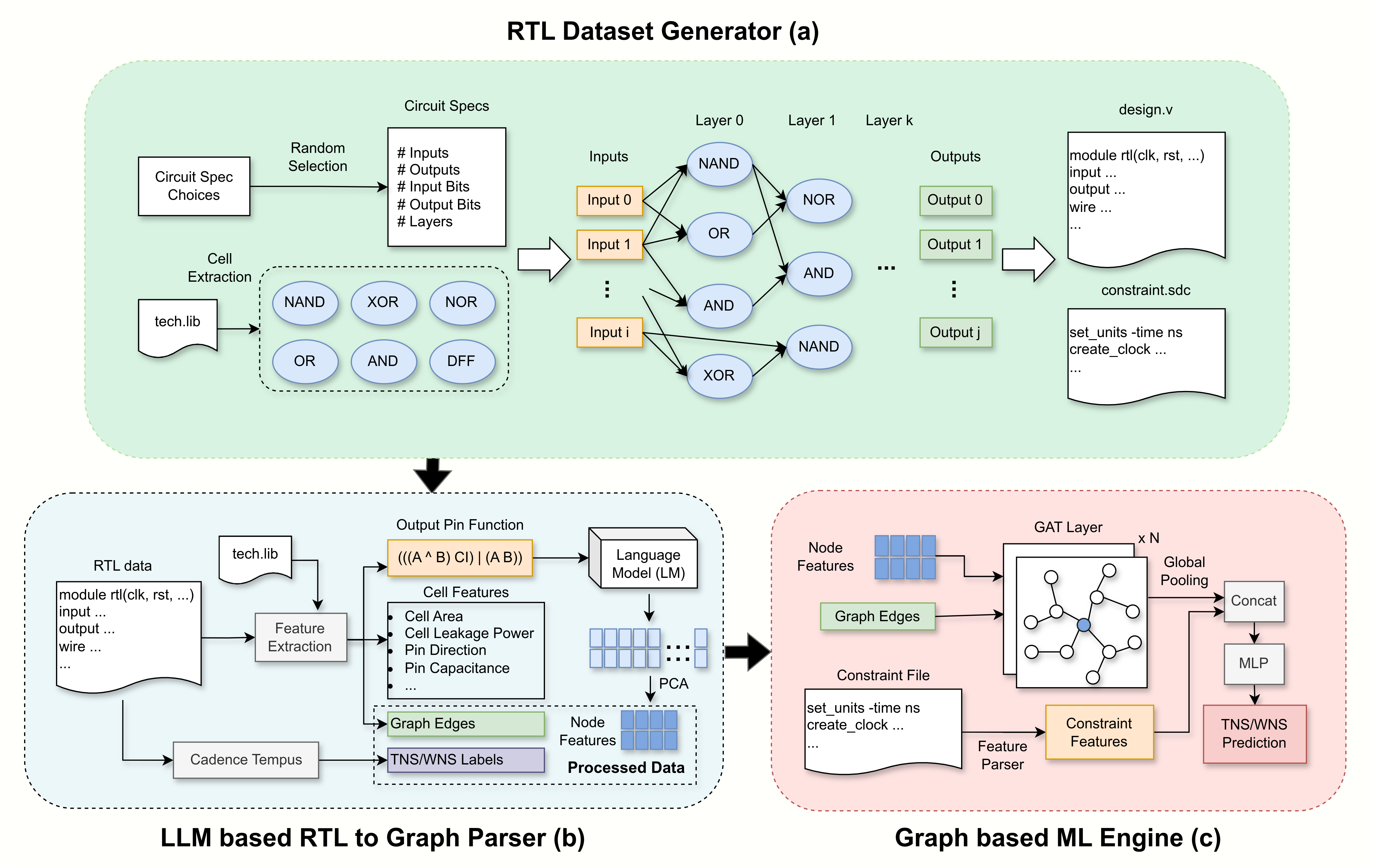

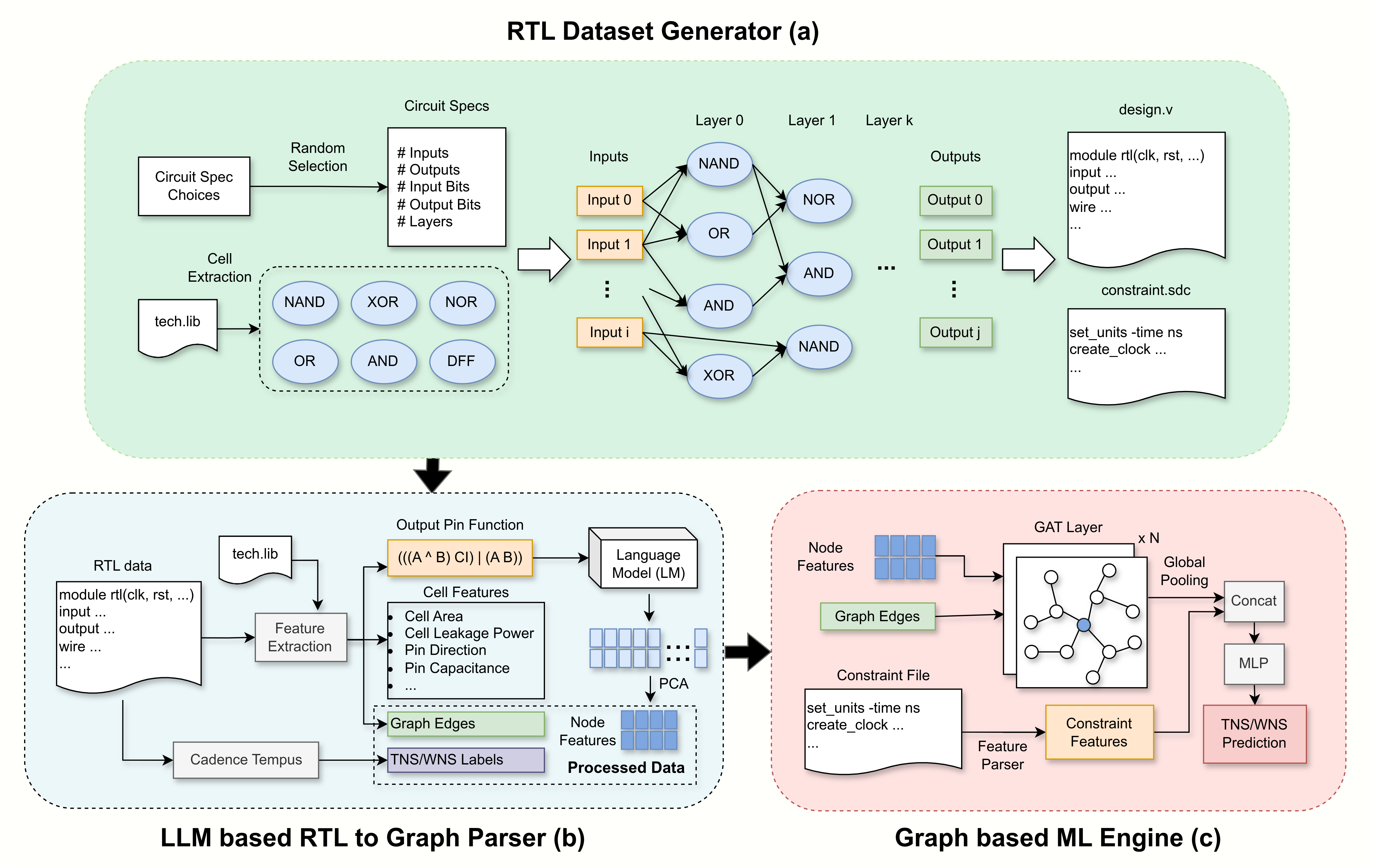

ASPDAC

ASPDAC

Graph-Based Timing Prediction at Early-Stage RTL Using Large Language Model

F.R. Amik, Y. Safari, Z. Zhang, B. Vaisband

Asia and South Pacific Design Automation Conference (ASPDAC) 2025

Developed an RTL dataset generator and utilized LLemma-7B to generate embeddings for graph-based timing prediction at early-stage RTL design.

ASPDAC

ASPDAC

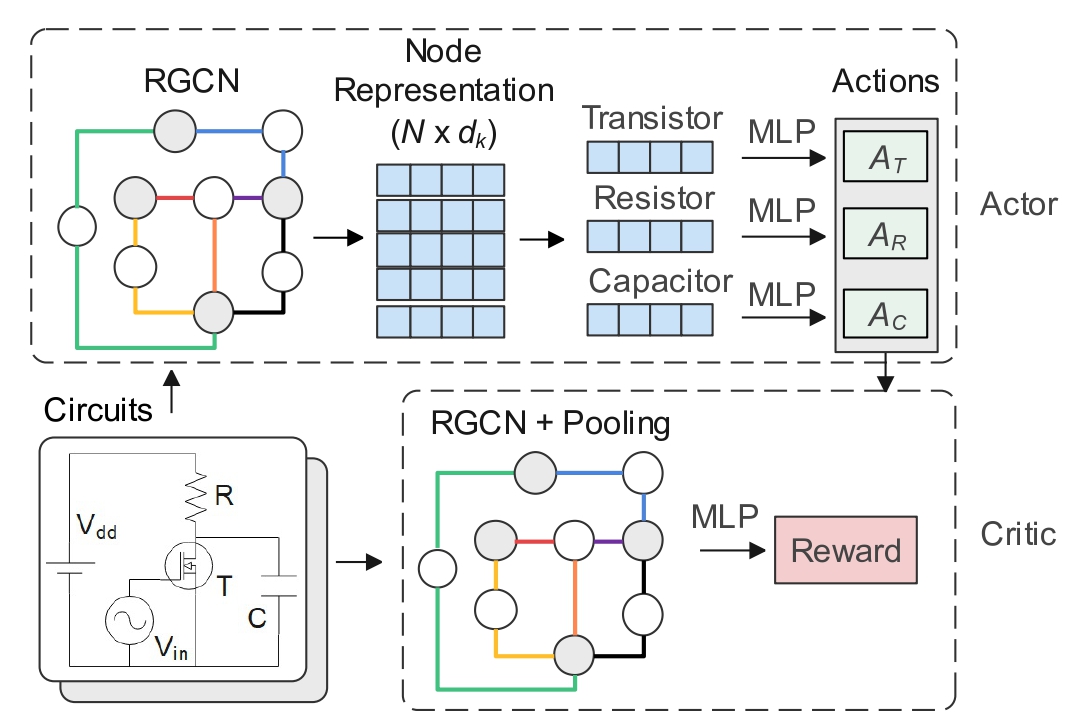

GLSVLSI

GLSVLSI

Generalizable and Relation Sensitive Netlist Representation for Analog Circuit Design

S. Penmetsa, F.R. Amik, Z. Zhang, et al.

34th Great Lakes Symposium on VLSI (GLSVLSI) 2024

Proposed a novel heterogeneous graph representation for analog circuits with enhanced generalization and knowledge transferability.

GLSVLSI

GLSVLSI